CPUs

SK hynix and TSMC announced early on Friday that they had signed a memorandum of understanding to collaborate on developing the next-generation HBM4 memory and advanced packaging technology. The initiative is designed to speed up the adoption of HBM4 memory and solidify SK hynix's and TSMC's leading positions in high-bandwidth memory and advanced processor applications. The primary focus of SK hynix's and TSMC's initial efforts will be to enhance the performance of the HBM4 stack's base die, which (if we put it very simply) acts like an ultra-wide interface between memory devices and host processors. With HBM4, SK hynix plans to use one of TSMC's advanced logic process technologies to build base dies to pack additional features and I/O pins within the confines of existing...

It’s Official: NVIDIA To Acquire Arm For $40 Billion

Following a number of rumors and leaks, NVIDIA this evening announced that it is buying Arm Limited for $40 billion. The cash and stock deal will see NVIDIA buy...

140 by Ryan Smith on 9/13/2020AMD Announces Ryzen "Zen 3" and Radeon "RDNA2" Presentations for October: A New Journey Begins

AMD today has announced that they will be making a pair of consumer product presentations in October. The chipmaker, who has been fairly quiet since the spring, will be...

145 by Ryan Smith on 9/9/2020Intel Launches 11th Gen Core Tiger Lake: Up to 4.8 GHz at 50 W, 2x GPU with Xe, New Branding

In August, Intel ran one of its rare Architecture Days where the company went into some detail about its upcoming Tiger Lake processor. This included target markets, core counts...

349 by Dr. Ian Cutress on 9/2/2020Intel Launches Tiger Lake: A Live Blog (Noon ET, 9am PT)

Intel is about to launch Tiger Lake. Follow along with our Live Blog!

54 by Dr. Ian Cutress on 9/2/20203DFabric: The Home for TSMC’s 2.5D and 3D Stacking Roadmap

Interposers. EMIB. Foveros. Die-to-die stacking. ODI. AIB.TSVs. All these words and acronyms have one overriding feature – they are all involved in how two bits of silicon physically connect...

9 by Dr. Ian Cutress on 9/2/2020Marvell Refocuses Thunder Server Platforms Towards Custom Silicon Business

Yesterday during Marvell’s quarterly earnings call, the company had made a surprise announcement that they are planning to restructure their server processor development team towards fully custom solutions, abandoning...

42 by Andrei Frumusanu on 8/28/2020TSMC Launches New N12e Process: FinFET at 0.4V for IoT

One of the main drivers for the semiconductor industry is the growth in always-connected devices that require silicon inside, either for compute, communication, or control. The ‘Internet of Things&rsquo...

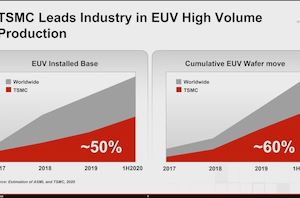

27 by Dr. Ian Cutress on 8/27/2020TSMC: We have 50% of All EUV Installations, 60% Wafer Capacity

One of the overriding central messages to TSMC’s Technology Symposium this week is that the company is a world leader in semiconductor manufacturing, especially at the leading edge process...

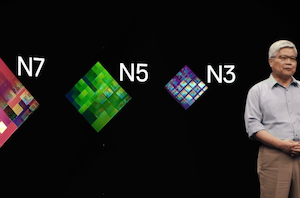

32 by Dr. Ian Cutress on 8/27/2020Where are my GAA-FETs? TSMC to Stay with FinFET for 3nm

As we passed that 22nm to 16nm barrier, almost all the major semiconductor fabrication companies on the leading edge transitioned from planar transistors to FinFET transistors. The benefits of...

37 by Dr. Ian Cutress on 8/26/2020TSMC Expects 5nm to be 11% of 2020 Wafer Production (sub 16nm)

One of the measures of how quickly a new process node gains traction is by comparing how many wafers are in production, especially as that new process node goes...

13 by Dr. Ian Cutress on 8/25/2020TSMC Teases 12-High 3D Stacked Silicon: SoIC Goes Extreme

I’ve maintained for a couple of years now that the future battleground when it comes to next-generation silicon is going to be in the interconnect – implicitly this relies...

15 by Dr. Ian Cutress on 8/25/2020TSMC Updates on Node Availability Beyond Logic: Analog, HV, Sensors, RF

Most of the time when we speak about semiconductor processes, we are focused on the leading edge of what is possible. Almost exclusively that leading edge is designed for...

3 by Dr. Ian Cutress on 8/25/2020‘Better Yield on 5nm than 7nm’: TSMC Update on Defect Rates for N5

One of the key metrics on how well a semiconductor process is developing is looking at its quantitative chip yield – or rather, its defect density. A manufacturing process...

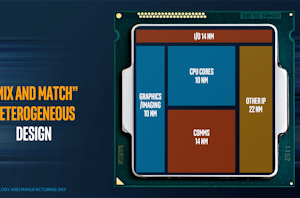

107 by Dr. Ian Cutress on 8/25/2020Intel Moving to Chiplets: ‘Client 2.0’ for 7nm

One of the more esoteric elements of Intel’s Architecture Day 2020 came very near the end, where Intel spent a few minutes discussing what it believes is the future...

67 by Dr. Ian Cutress on 8/21/2020Cerebras Wafer Scale Engine News: DoE Supercomputer Gets 400,000 AI Cores

One of the more interesting AI silicon projects over the last couple of years has been the Cerebras Wafer Scale Engine, most notably for the fact that a single...

8 by Dr. Ian Cutress on 8/21/2020342 Transistors for Every Person In the World: Cerebras 2nd Gen Wafer Scale Engine Teased

One of the highlights of Hot Chips from 2019 was the startup Cerebras showcasing its product – a large ‘wafer-scale’ AI chip that was literally the size of a...

32 by Dr. Ian Cutress on 8/18/2020Hot Chips 2020 Live Blog: Microsoft Xbox Series X System Architecture (6:00pm PT)

Hot Chips has gone virtual this year! Lots of talks on lots of products, including Tiger Lake, Xe, POWER10, Xbox Series X, TPUv3, and a special Raja Koduri Keynote...

59 by Dr. Ian Cutress on 8/17/2020Hot Chips 2020 Live Blog: Alibaba Xuantie-910 RISC-V CPU (3:00pm PT)

Hot Chips has gone virtual this year! Lots of talks on lots of products, including Tiger Lake, Xe, POWER10, Xbox Series X, TPUv3, and a special Raja Koduri Keynote...

6 by Dr. Ian Cutress on 8/17/2020Hot Chips 2020 Live Blog: Intel's Raja Koduri Keynote (2:00pm PT)

Hot Chips has gone virtual this year! Lots of talks on lots of products, including Tiger Lake, Xe, POWER10, Xbox Series X, TPUv3, and a special Raja Koduri Keynote...

19 by Dr. Ian Cutress on 8/17/2020Hot Chips 2020: Marvell Details ThunderX3 CPUs - Up to 60 Cores Per Die, 96 Dual-Die in 2021

Today as part of HotChips 2020 we saw Marvell finally reveal some details on the microarchitecture of their new ThunderX3 server CPUs and core microarchitectures. The company had announced...

27 by Andrei Frumusanu on 8/17/2020