AMD Zen 3 Ryzen Deep Dive Review: 5950X, 5900X, 5800X and 5600X Tested

by Dr. Ian Cutress on November 5, 2020 9:01 AM ESTCPU Tests: Simulation

Simulation and Science have a lot of overlap in the benchmarking world, however for this distinction we’re separating into two segments mostly based on the utility of the resulting data. The benchmarks that fall under Science have a distinct use for the data they output – in our Simulation section, these act more like synthetics but at some level are still trying to simulate a given environment.

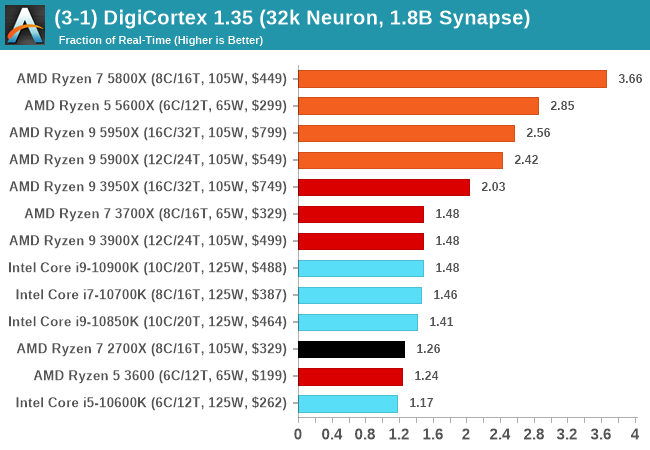

DigiCortex v1.35: link

DigiCortex is a pet project for the visualization of neuron and synapse activity in the brain. The software comes with a variety of benchmark modes, and we take the small benchmark which runs a 32k neuron/1.8B synapse simulation, similar to a small slug.

The results on the output are given as a fraction of whether the system can simulate in real-time, so anything above a value of one is suitable for real-time work. The benchmark offers a 'no firing synapse' mode, which in essence detects DRAM and bus speed, however we take the firing mode which adds CPU work with every firing.

The software originally shipped with a benchmark that recorded the first few cycles and output a result. So while fast multi-threaded processors this made the benchmark last less than a few seconds, slow dual-core processors could be running for almost an hour. There is also the issue of DigiCortex starting with a base neuron/synapse map in ‘off mode’, giving a high result in the first few cycles as none of the nodes are currently active. We found that the performance settles down into a steady state after a while (when the model is actively in use), so we asked the author to allow for a ‘warm-up’ phase and for the benchmark to be the average over a second sample time.

For our test, we give the benchmark 20000 cycles to warm up and then take the data over the next 10000 cycles seconds for the test – on a modern processor this takes 30 seconds and 150 seconds respectively. This is then repeated a minimum of 10 times, with the first three results rejected. Results are shown as a multiple of real-time calculation.

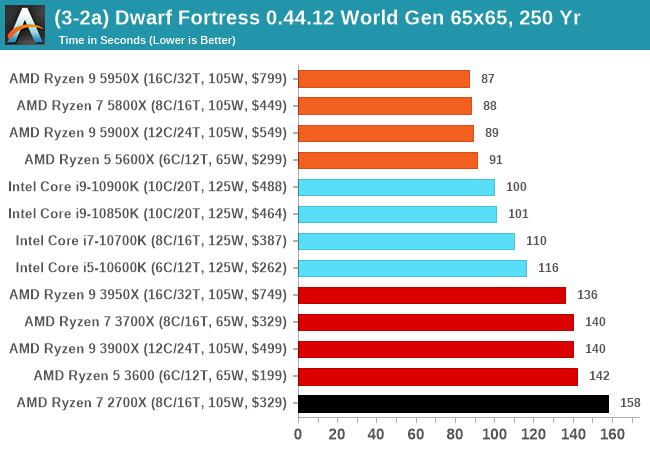

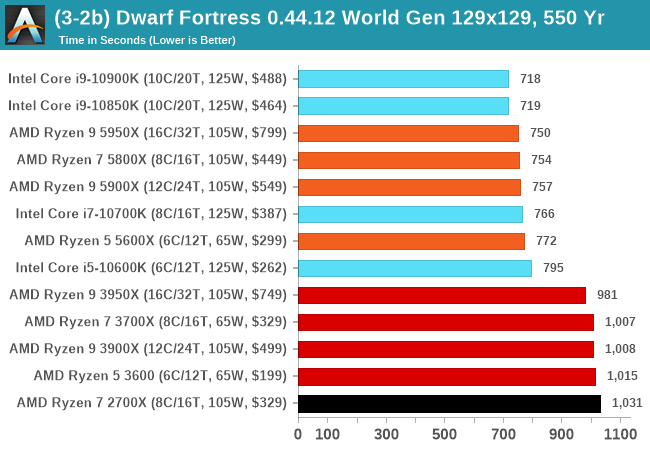

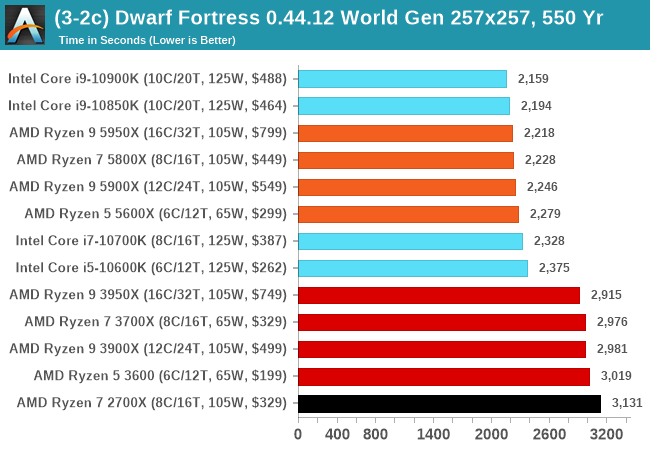

Dwarf Fortress 0.44.12: Link

Another long standing request for our benchmark suite has been Dwarf Fortress, a popular management/roguelike indie video game, first launched in 2006 and still being regularly updated today, aiming for a Steam launch sometime in the future.

Emulating the ASCII interfaces of old, this title is a rather complex beast, which can generate environments subject to millennia of rule, famous faces, peasants, and key historical figures and events. The further you get into the game, depending on the size of the world, the slower it becomes as it has to simulate more famous people, more world events, and the natural way that humanoid creatures take over an environment. Like some kind of virus.

For our test we’re using DFMark. DFMark is a benchmark built by vorsgren on the Bay12Forums that gives two different modes built on DFHack: world generation and embark. These tests can be configured, but range anywhere from 3 minutes to several hours. After analyzing the test, we ended up going for three different world generation sizes:

- Small, a 65x65 world with 250 years, 10 civilizations and 4 megabeasts

- Medium, a 127x127 world with 550 years, 10 civilizations and 4 megabeasts

- Large, a 257x257 world with 550 years, 40 civilizations and 10 megabeasts

DFMark outputs the time to run any given test, so this is what we use for the output. We loop the small test for as many times possible in 10 minutes, the medium test for as many times in 30 minutes, and the large test for as many times in an hour.

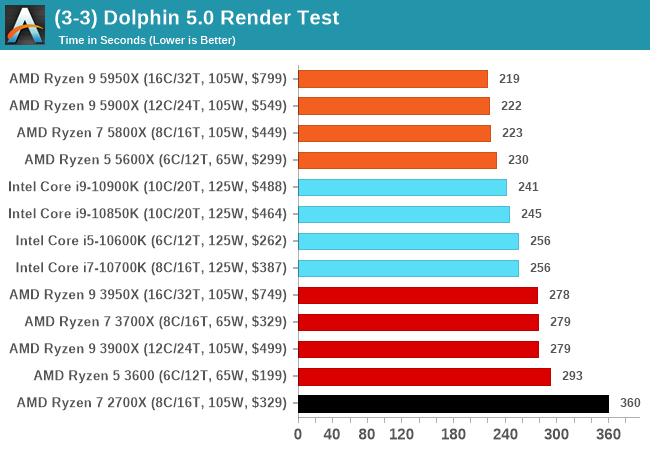

Dolphin v5.0 Emulation: Link

Many emulators are often bound by single thread CPU performance, and general reports tended to suggest that Haswell provided a significant boost to emulator performance. This benchmark runs a Wii program that ray traces a complex 3D scene inside the Dolphin Wii emulator. Performance on this benchmark is a good proxy of the speed of Dolphin CPU emulation, which is an intensive single core task using most aspects of a CPU. Results are given in seconds, where the Wii itself scores 1051 seconds.

339 Comments

View All Comments

Spunjji - Sunday, November 8, 2020 - link

True, that combo will rockSpunjji - Sunday, November 8, 2020 - link

Why is 100 watts extra power to get that performance suddenly NBD?CrystalCowboy - Thursday, November 5, 2020 - link

If they would die-shrink that I/O chiplet, they might have room for a third CCD...adt6247 - Thursday, November 5, 2020 - link

Then most motherboards would likely have a hard time with power delivery for 8 additional cores.Also, a the IO die only supports 2 CCDs -- doesn't have the lanes for more. Hence the Threadripper parts with 4 CCDs being NUMA devices -- two CCDs with direct access to RAM, and two without.

lmcd - Thursday, November 5, 2020 - link

Also package size constraints have about just as much to do with pin count. Necessary pin count for supporting 2 more CCDs' worth of bandwidth and power (regardless of board's ability to supply it) pushes AMD entirely out of the ITX motherboard market (barring absolutely insane designs that cost $300-400 for minimum features beyond turning on). And any situation using more than 16 cores needs more bandwidth, so the pin count increase -> no ITX is really a no-go.AntonErtl - Thursday, November 5, 2020 - link

The IO die supports 4 CCXs on the 3900X and 3950X. It seems that a CCD does not get a wider port than a CCX (the ports for Zen3 do not seem particularly wide at 16B/cycle in write width), so it may be possible to connect 4 CCDs to the IO die. Whether that will physically fit, or will be too RAM-bandwidth limited is then the question. But given that Intel cannot even match the 16 cores, there is little competetive pressure to put more cores in AM4.schujj07 - Friday, November 6, 2020 - link

Any single socket Zen 2 device is seen as a single NUMA node. When you talk about 1st & 2nd Gen Threadripper, yes they were seen as 2 or 4 NUMA nodes depending on the number of cores due to how the architecture was made.nandnandnand - Thursday, November 5, 2020 - link

Zen 4 core chiplets will be shrunk to 5nm, on a new AM5 socket that could have larger dimensions. And maybe the I/O chiplet will shrink to 7nm at the same time.I expect 3x 8-core chiplets or 2x 12-core chiplets. A graphics chiplet for all desktop models is possible. If so, maybe 12-core chiplets are the way to go.

smilingcrow - Thursday, November 5, 2020 - link

With only dual channel RAM there will be an issue with performance scaling beyond a certain number of cores.It seems as if the sixteen core part already scales poorly with some workloads, so adding fifty percent more is not great.

Leave that for TR.

phoenix_rizzen - Thursday, November 5, 2020 - link

Yeah, it seems like 1 memory channel for every 8 cores is the sweet spot. At least with DDR4 memory controllers.