Intel Unveils Lunar Lake Architecture: New P and E cores, Xe2-LPG Graphics, New NPU 4 Brings More AI Performance

by Gavin Bonshor on June 3, 2024 11:00 PM ESTIntel Lunar Lake: New E-Core, Skymont Takes Flight For Peak Efficiency

Intel also opts for their Skymont E-cores, which are designed more for efficiency while maintaining a solid level of performance at a lower power envelope.

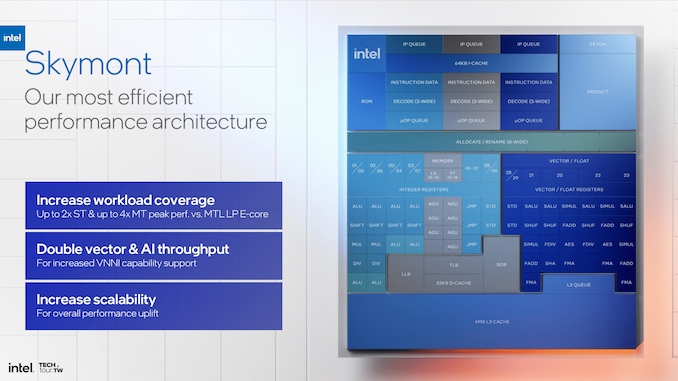

The Skymont cores feature a significantly broader decode architecture, with a 9-wide decode stage that includes 50% more decode clusters than previous generations. This is supported by a larger micro-op queue, which now holds 96 entries compared to 64 in the previous Crestmont E-Cores.

Intel has improved the out-of-order execution engine by boosting the allocation width from 4 to 8 and the retire width from 8 to 16. The next-gen Skymont core is supposed to surpass Crestmont E-Cores with double the allocation and retire width in terms of its ability to commit and run out-of-order instructions, decreasing overall latency and minimizing stalling for data dependencies.

Queuing and buffering capabilities have also been improved within the Skymont E-Core. It features a deeper reorder buffer of 416 entries, up from the previous 256, while Intel claims the size of the physical register files (PRF) and INT, MEM, and Vectors have been made deeper, too.

Focusing on dispatch ports, Intel has opted for a similar approach to Crestmont. This includes 26 dispatch ports, 8 integer ALUs, 3 Jump Ports, and 3 for load operations per cycle. Regarding Vector performance, Skymont supports 4x128-bit FP and SIMD vectors, which doubles gigaflops/TOPs and reduces latency for floating-point operations.

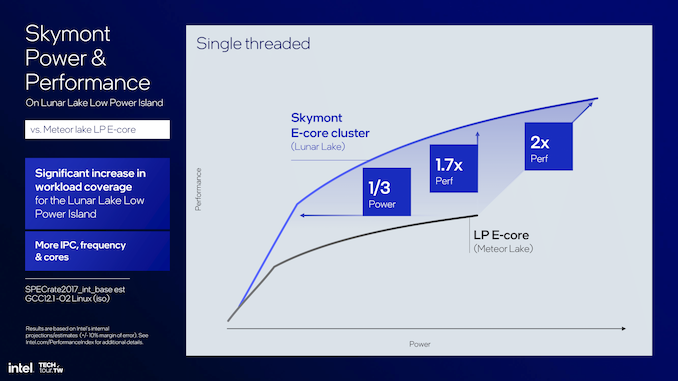

Intel does provide some figures highlighting Skymont's power efficiency and performance when compared directly to the Low Power Island E-Cores included on the SoC tile on Meteor Lake. In this particular line chart, Intel increases single-threaded performance by 1.7X while consuming just one-third of the power relative to Meteor Lake's LP E-cores.

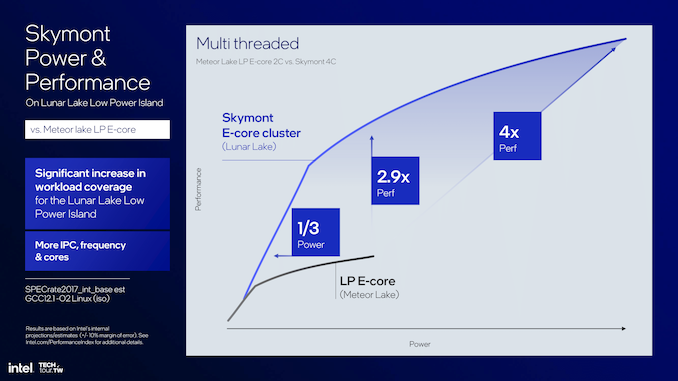

Looking at multi-threaded performance, Intel puts Skymont 2.9X faster at 1/3rd of the power requirements when compared to Meteor Lake and the LP E-cores. It's worth noting that the Skymont E-Core cluster on the compute tile has double the cores of the Meteor Lake LP E-Core cluster (4 vs. 2), so performance is expected to be higher overall.

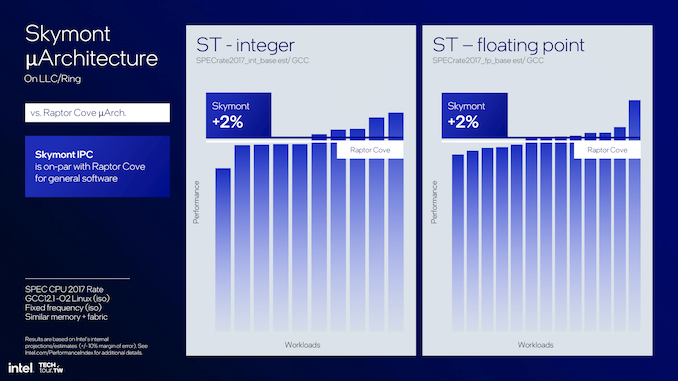

Due to their low-powered nature for mobile devices such as notebooks, the Skymont E-cores are designed to be very flexible, with some leverage over previous E-Core architectures. Compared to Raptor Cove, Skymont offers 2% better integer and floating-point performance in single-threaded workloads, with a power and thermal envelope almost identical to Raptor Cove. This is in a more desktop-friendly environment, as Intel does depict the data with the Skymont cores on an LLC or a Ring Bus. This is E-Cores versus the previous gen of P-Cores, in which Intel is claiming a 2% lead.

Intel's Skymont E-cores represent the next leap in Intel's architectural development. According to Intel's disclosure, Skymont looks to be a marked improvement in multiple areas over the previous Crestmont E-Core, including decoding, execution, memory subsystems, and power efficiency. While Intel discloses them as E-Cores, the messaging surrounding Skymont is a little confusing.

The easiest way to decipher this is that they are similar to the two LP E-Cores within the Meteor Lake SoC tile, but with Lunar Lake, they are in a cluster of four built onto the compute tile. On Lunar Lake, they will be as efficient as the LP E-cores of old, but for desktop, they will be in a cluster on the chips Ring Bus, meaning they will likely be similar to the traditional E-cores we've seen before with Intel's 14th/13th/12th Gen Core families.

90 Comments

View All Comments

Ryan Smith - Tuesday, June 4, 2024 - link

"Was there a deadline push to get it out as soon as Intel released the information on Lunar Lake?"Yes. There was a hard deadline on this. Copyediting is ongoing. Reply

Drumsticks - Tuesday, June 4, 2024 - link

Thank you for responding. I hope there’s an opportunity to address some of the writing at a bare minimum and maybe inject some of your own voice.Lunar Lake honestly looks like a pretty big deal. The process is great, the microarchs seem impressive on paper, and it’s coming out to market within a quarter of when it needs to, not within three years. Looking forward to deeper analysis and comparisons, wherever they come from, when the time comes. Reply

NetMage - Tuesday, June 4, 2024 - link

A deadline for what? To regurgitate Intel PR hype as an LLM enhanced unreadable English as a second language article before everyone else publishes their copy of Intel’s Press Release? This article should have never been published.The Xe2 page is particularly horrendous. Reply

Terry_Craig - Thursday, June 6, 2024 - link

There's nothing particularly interesting about Lunar Lake that deserves all this hunger for high-quality content. Replymode_13h - Friday, June 7, 2024 - link

Sarcasm detected. Replyeastcoast_pete - Tuesday, June 4, 2024 - link

Now, I also like good copy editing, but this kind of coverage is done almost in real time. That, plus the time zone difference makes it hard to have a fully copy-edited and proofed article posted, all within hours of the presentation. ReplyDrumsticks - Wednesday, June 5, 2024 - link

I understand that. Anandtech has done it in the past, and produced really stellar coverage that way. I'm a little surprised that some of the paragraphs haven't gotten complete, proper rewrites more than 36 hours after the article went live. (To be fair, that's one business day really). But it's a headliner article on their front page; I'd hoped for more love. Replyskavi - Tuesday, June 4, 2024 - link

Thank you for writing this out. Similar feelings, but I could not have put it so well. Here’s hoping AnandTech can figure out how to get back to that level of quality. ReplyStrom- - Tuesday, June 4, 2024 - link

I loved reading about the benefits of Thunderbolt 5. ReplyEthiaW - Tuesday, June 4, 2024 - link

Well done Intel, receiving enormous CHIPS subsidy while hollowing out production to TSMC tile by tile. Reply