Intel Unveils Lunar Lake Architecture: New P and E cores, Xe2-LPG Graphics, New NPU 4 Brings More AI Performance

by Gavin Bonshor on June 3, 2024 11:00 PM ESTIntel Lunar Lake: New E-Core, Skymont Takes Flight For Peak Efficiency

Intel also opts for their Skymont E-cores, which are designed more for efficiency while maintaining a solid level of performance at a lower power envelope.

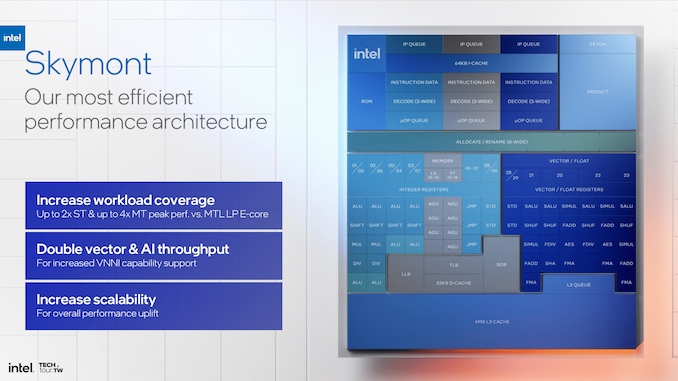

The Skymont cores feature a significantly broader decode architecture, with a 9-wide decode stage that includes 50% more decode clusters than previous generations. This is supported by a larger micro-op queue, which now holds 96 entries compared to 64 in the previous Crestmont E-Cores.

Intel has improved the out-of-order execution engine by boosting the allocation width from 4 to 8 and the retire width from 8 to 16. The next-gen Skymont core is supposed to surpass Crestmont E-Cores with double the allocation and retire width in terms of its ability to commit and run out-of-order instructions, decreasing overall latency and minimizing stalling for data dependencies.

Queuing and buffering capabilities have also been improved within the Skymont E-Core. It features a deeper reorder buffer of 416 entries, up from the previous 256, while Intel claims the size of the physical register files (PRF) and INT, MEM, and Vectors have been made deeper, too.

Focusing on dispatch ports, Intel has opted for a similar approach to Crestmont. This includes 26 dispatch ports, 8 integer ALUs, 3 Jump Ports, and 3 for load operations per cycle. Regarding Vector performance, Skymont supports 4x128-bit FP and SIMD vectors, which doubles gigaflops/TOPs and reduces latency for floating-point operations.

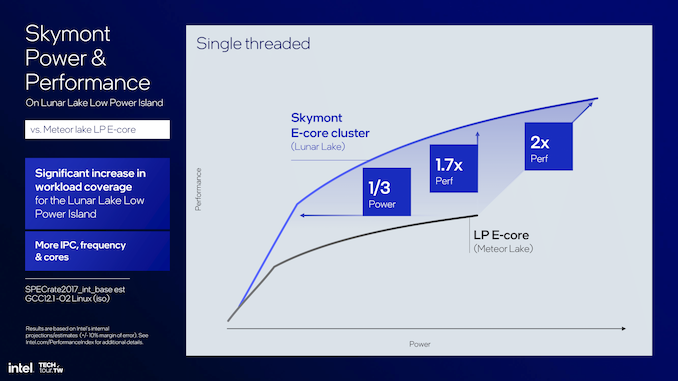

Intel does provide some figures highlighting Skymont's power efficiency and performance when compared directly to the Low Power Island E-Cores included on the SoC tile on Meteor Lake. In this particular line chart, Intel increases single-threaded performance by 1.7X while consuming just one-third of the power relative to Meteor Lake's LP E-cores.

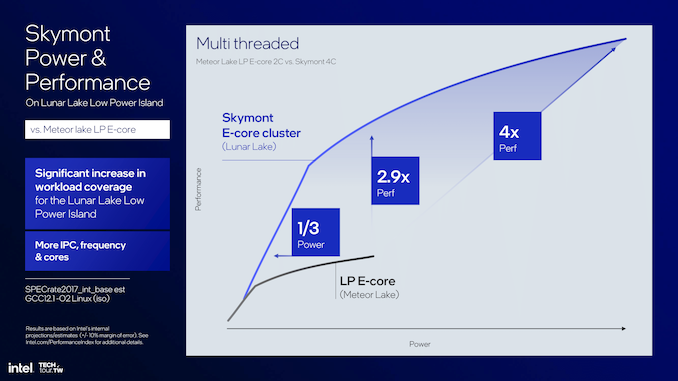

Looking at multi-threaded performance, Intel puts Skymont 2.9X faster at 1/3rd of the power requirements when compared to Meteor Lake and the LP E-cores. It's worth noting that the Skymont E-Core cluster on the compute tile has double the cores of the Meteor Lake LP E-Core cluster (4 vs. 2), so performance is expected to be higher overall.

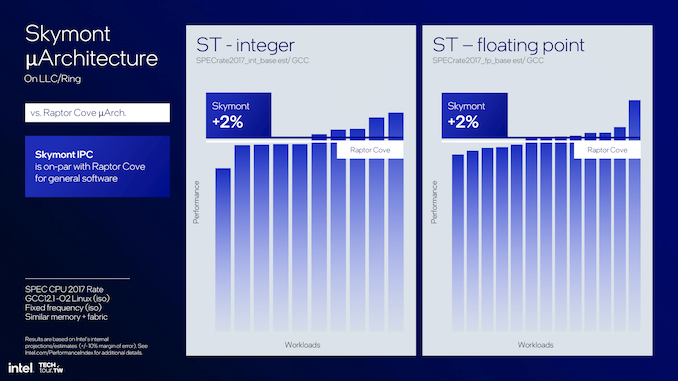

Due to their low-powered nature for mobile devices such as notebooks, the Skymont E-cores are designed to be very flexible, with some leverage over previous E-Core architectures. Compared to Raptor Cove, Skymont offers 2% better integer and floating-point performance in single-threaded workloads, with a power and thermal envelope almost identical to Raptor Cove. This is in a more desktop-friendly environment, as Intel does depict the data with the Skymont cores on an LLC or a Ring Bus. This is E-Cores versus the previous gen of P-Cores, in which Intel is claiming a 2% lead.

Intel's Skymont E-cores represent the next leap in Intel's architectural development. According to Intel's disclosure, Skymont looks to be a marked improvement in multiple areas over the previous Crestmont E-Core, including decoding, execution, memory subsystems, and power efficiency. While Intel discloses them as E-Cores, the messaging surrounding Skymont is a little confusing.

The easiest way to decipher this is that they are similar to the two LP E-Cores within the Meteor Lake SoC tile, but with Lunar Lake, they are in a cluster of four built onto the compute tile. On Lunar Lake, they will be as efficient as the LP E-cores of old, but for desktop, they will be in a cluster on the chips Ring Bus, meaning they will likely be similar to the traditional E-cores we've seen before with Intel's 14th/13th/12th Gen Core families.

90 Comments

View All Comments

mode_13h - Tuesday, June 4, 2024 - link

Yeah, it definitely comes across as two-faced for Intel to be pitching its foundry business to others, while it's not even using it for its own cutting-edge CPUs! Replykn00tcn - Tuesday, June 4, 2024 - link

1) bob (or brian?) made a deal with tsmc and they need fill the required capacity2) tsmc chiplet packaging requires all tiles to come from tsmc (but mixing tile foundries is fine as long as someone else packages)

3) lunar lake isnt high power high core desktop/server, there's plenty else to make themselves, and obviously they've been ramping cutting edge future nodes

4) these things take years, why would a recent subsidy relate to old deals Reply

mode_13h - Thursday, June 6, 2024 - link

> 1) bob (or brian?) made a deal with tsmc and they need fill the required capacityThis is probably the dumbest claim I've seen in a while. There's guaranteed to be an escape clause in that contract, although Intel would be stuck with some fee.

Given the current demand for cutting-edge nodes, I'm sure Intel could probably work out an agreement with another fab customer to buy their excess wafer capacity and probably even turn a profit by it.

> 2) tsmc chiplet packaging requires all tiles to come from tsmc

Second dumbest claim in the thread. Lunar Lake uses Foveros, not TSMC's technology, and Intel is making the base layer on their own 22 nm node.

> 3) lunar lake isnt high power high core desktop/server

What does that have to do with anything? It still needs to compete on performance and efficiency!

> why would a recent subsidy relate to old deals

Who said anything about that? Reply

kwohlt - Tuesday, June 4, 2024 - link

Intel's foundry service doesn't have a full suite of nodes to choose from and is currently building out a fabs. In the meantime, client will be using some of the TSMC N3B allocation that Intel carved out years ago. Expect 2024-2025 to be peak TSMC usage.What other options were realistically available? Intel 3 is just hitting the market and fully allocated to Xeon 6 initially. Intel 4 isn't library complete and wouldn't work for a tile that also contains NPU and GPU. Intel 7 is heavy DTCO'd for ADL/RPL and has poor low wattage performance. 18A isn't ready yet.

By the time 14A releases, Intel will have a selection of 18A and the Intel 3 family of nodes to pick from for their other CPU tiles. Reply

mode_13h - Thursday, June 6, 2024 - link

> Intel 3 is just hitting the market and fully allocated to Xeon 6 initiallyThe Lunar Lake CPU tiles can't be very big. They should've been a good "pipe cleaner" product for Intel to ramp up their "3" node, before making the huge Xeon dies.

I hadn't noticed the GPU was on the same tile. If true, I think they could've kept it on its own tile, as Meteor Lake did. Reply

lmcd - Wednesday, June 12, 2024 - link

Intel has not shipped an Xe product on an Intel process since DG1. We don't know that it ports.Adding a separate die might have increased the package size, and part of the point of this product was to be a small package that could supplant Qualcomm designs easily (and the PMIC callout was specifically targeted at vendors that got burned by Qualcomm's power shenanigans, if you believe Charlie). Reply

andrewaggb - Thursday, June 6, 2024 - link

yeah, it's not a great look on the fab side, but honestly I hope it's an amazing chip and worth upgrading. I hope Qualcomm's chip is great as well and get some actual innovation/competition going on. Replyeonsim - Tuesday, June 4, 2024 - link

Is Intel comparing there new E-cores to the LP-E cores here (the ones on the SoC with no L3), rather than the main E-cores for Meteor lake? Replymode_13h - Tuesday, June 4, 2024 - link

+1 Replyname99 - Wednesday, June 5, 2024 - link

Exactly.And judging from what I've seen on the internet, plenty of people were fooled. And don't like to be told that they were fooled... Reply