Intel Unveils Lunar Lake Architecture: New P and E cores, Xe2-LPG Graphics, New NPU 4 Brings More AI Performance

by Gavin Bonshor on June 3, 2024 11:00 PM ESTBetter I/O: Thunderbolt 4, Thunderbolt Share, Wi-Fi 7 Included

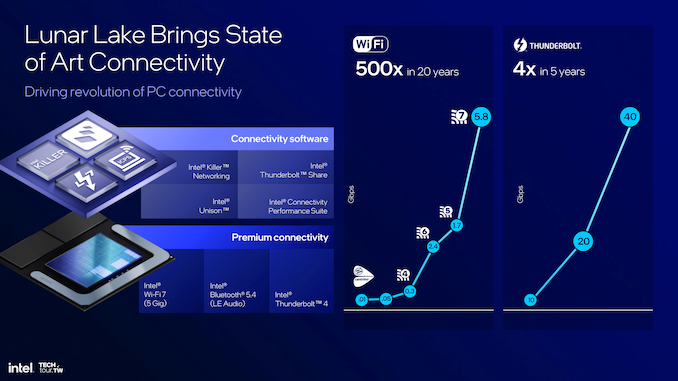

Intel's developments in I/O and connectivity bring the current generation of connectivity to the Lunar Lake platform. Key highlights in terms of I/O, which is set for Lunar Lake, include native Thunderbolt 4 connectivity, the new Thunderbolt Share functionality, and the upgrade to Wi-Fi 7 wireless connectivity.

Thunderbolt 4 builds excellently on the foundation laid by Thunderbolt 3, which isn't new from a controller standpoint. It does offer enhancements in connectivity and bandwidth, and being internally opted for is the key difference here. Three Thunderbolt ports are now allowed for every laptop, making this feature very flexible and usable.

Thunderbolt Share is a new technology that will come with Lunar Lake. It allows multiple PCs to share screens, monitors, keyboards, mice, and storage across systems in a straightforward and fast manner at up to 60 frames per second. This is very important in collaborative environments, whereby sharing data is made easy and quick, thus improving workflow. When used in productivity tasks, the utility allows users to sync folders and has a drag-and-drop file-sharing function between PCs at high speeds.

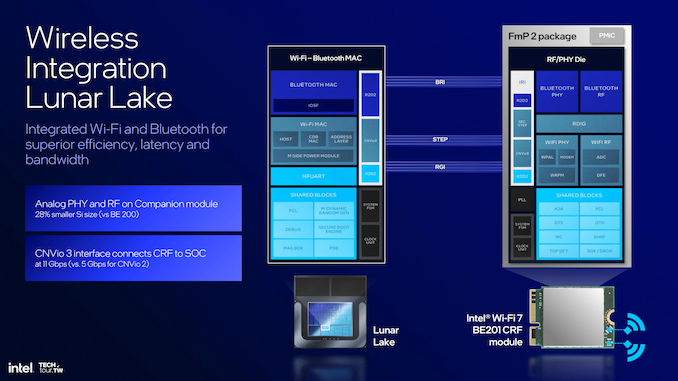

Wi-Fi 7 is also integrated into the Lunar Lake platform, which Meteor Lake omitted regarding wireless connectivity. This multi-link operation feature of Wi-Fi 7 adds wireless signal integrity and reliability and increases throughput with less latency by duplicating packets across all links above. This implies smoother performance and better load balancing, even in demanding applications. The greatest benefit from Wi-Fi 7's new capabilities comes to the user when dealing with bandwidth-intensive tasks.

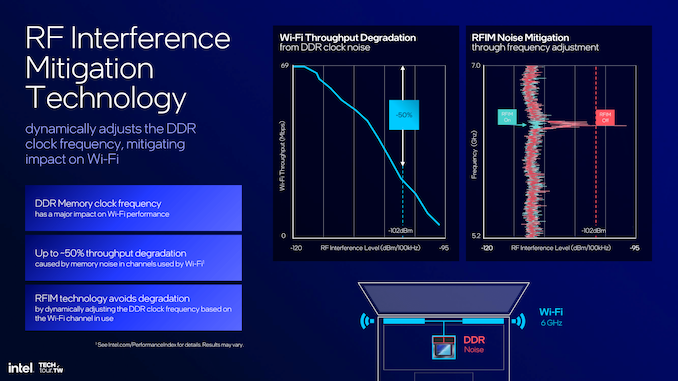

It also includes RF Interference Mitigation technology, where the DDR clock frequency is automatically tuned to minimize interference with Wi-Fi signals. This function saves 50% of throughput degradation caused by memory noise; thus, theoretically, it should uplift the performance of the entire wireless network. Another positive effect users can expect is robust connectivity, even in very demanding environments.

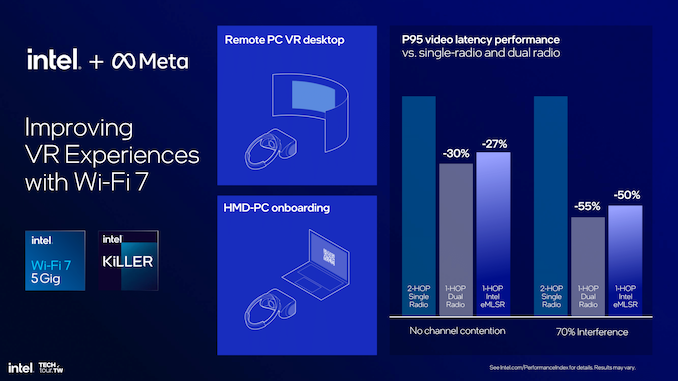

Intel's partnership with Meta goes further, tapping into this Wi-Fi 7 technology to enhance VR experiences. This further optimizes the video latency performance and reduces interference, thus making VR applications more seamless and engaging, at least from a wireless connectivity viewpoint. The new enhancements of Wi-Fi 7 offer high, reliable speed with low latency to meet the most challenging needs in VR applications.

91 Comments

View All Comments

thestryker - Monday, June 3, 2024 - link

I'm curious what the overall E-core performance is going to look like since the cluster won't have L3 cache access. Chips and Cheese did some analysis of the LP E-cores on MTL and found this specifically to be a big negative. I'm guessing this design is going to be limited to just LNL and is predominantly for the power savings.ET - Tuesday, June 4, 2024 - link

Interestingly, Intel is comparing Skymont to Raptor Cover. I agree that we have to wonder how the L3 (or lack thereof) affect this, but from the Chips and Cheese figures alongside Intel's performance improvement figures, it looks like Skymont without L3 cache will be faster than Crestmont with L3 cache.kwohlt - Tuesday, June 4, 2024 - link

There's 8MB of "SOC cache", separate from both the P and E cores, that should in practice function as the E cores' L3thestryker - Tuesday, June 4, 2024 - link

That's my assumption as well as I think the GPU would be the other part predominantly using it and they shouldn't really both be hitting it at the same time.sharath.naik - Monday, June 10, 2024 - link

Side cache is not the same as L3, or I think they would have called it that. shared L3 is where the memory sync can happen across cores. if not, it needs to go all the way back to ram. So, side caches really cannot be considered as L3, more like expanded L2 for E-core and expanded l3 for P-Core? is my guess. Yes, it means things that run on both E-Core and P-Core, at the same time, will take a hit on performance. I think they were targeting the majority use case. where most won't need more than 4 threads or threads won't be working on the same data.powerarmour - Thursday, June 6, 2024 - link

I can see this being an embarrassing launch if it gets slapped around by Qualcomm's SDx Elitemode_13h - Friday, June 7, 2024 - link

Well, they're on a better node that Qualcomm, so there's that.sharath.naik - Monday, June 10, 2024 - link

It absolutely will. Because this is going to be slower than meteor lake in CPU. Elite is supposed to be 30% faster. Intel should have released 8 P-core version to compete in performance. But I think they wanted to reserve that to be produced on their own fabs.lmcd - Monday, June 17, 2024 - link

Snap Elite is supposed to be 30% faster at essentially-undisclosed power. Lunar Lake will ironically undercut the Snapdragon Elite on power and cost while delivering good performance.Drumsticks - Tuesday, June 4, 2024 - link

I hate to ask this, but was this article fully written by Gavin and proof'ed by another editor? Was there a deadline push to get it out as soon as Intel released the information on Lunar Lake? It just reads so, so disjointed. It feels like there are so many issues in this paragraph alone on the P-core overview; it feels jarring to read."This Lion Cove architecture **also aligns with performance increases**, boasting a predicted double-digit bump in IPC over the older Redwood Cove generation. This uplift is noticed, especially **in the betterment of its hyper-threading, whereby improved IPC** by 30%, dynamic power efficiency improved by 20%, **and previous technologies, in balancing**, without increasing the core area, **in a commitment of Intel to better performance**, within existing physical constraints."

I've seen so much better work from Gavin, and Anandtech in general, that I almost hope that this page was heavily written by software. I know it's a press release, and there's not a whole lot of information, but the level of first party detail here feels similar to the Architecture Day 2021 presentations Intel did on Alder Lake, which got fantastic coverage from Andrei and Dr. Cuttress, and here it feels like we are getting a poorly worded restating of the slides with hardly any analysis or greater than surface level understanding.

I've been reading Anandtech since I was 15, and the level of detail in the Sandy Bridge era articles honestly had a huge influence on my choice to pursue a career in CPU Design. I've mountains of respect for what Anandtech has published in the past, but this article feels rushed.