Intel's Silverthorne Unveiled: Detailing Baby Centrino

by Anand Lal Shimpi on February 20, 2008 12:00 AM EST- Posted in

- CPUs

Lower Power than Centrino

With mobile Penryn Intel introduced a new power state it calls C6. In the C6 power state the CPU is in a virtual reset state, and core voltage is very close to zero. The core clock, all of the PLLs, and caches are completely turned off. All of the state data is saved in a 10.5KB storage area, similar to mobile Penryn (but smaller since there's not as much state to save). Upon exiting C6 the processor's previous state is restored from this memory, called the C6 array. It takes around 100us to get out of C6, but the power savings are more than worth the effort - it's a similar approach of power for performance that we saw in the design of the original Pentium M processor.

Clock gating (sending the clock signal through a logic gate that can disable it on the fly, thus shutting off whatever the clock connects to) is an obvious aspect of Silverthorne's design. All Intel processors use clock gating; Silverthorne simply uses it more aggressively - the clock going to every "power zone" is gated, something that isn't the case in mobile Core 2. Each logic cluster (205 total) in Silverthorne is referred to as a Functional Unit Block (FUB) and the entire chip uses what Intel calls a sea of FUB design. Each FUB is clock gated and can be disabled independently to optimize for power consumption. The cache in Silverthorne is in its own FUB, which apparently isn't the case in mobile Core 2.

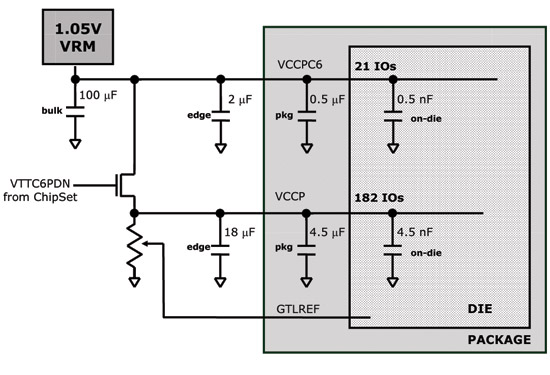

Keeping Silverthorne on life support, only 21 pins are necessary

Silverthorne uses a split power plane; in its deepest sleep state (C6) the chip can shut off all but 21 pins which are driven by the 1.05V VRM. By having two separate power planes the chip can manage power on a more granular level. While it can't disable individual pins, it can disable large groups of them leaving only 21 active when things like the L2 cache and bus interface are powered down.

Intel mentioned that Silverthorne will remain in its C6 sleep state 90% of the time. However, that figure is slightly misleading because it's only possible to remain in C6 when the CPU is completely idle. The 90% figure comes from taking into account a mobile device sitting in your pocket doing nothing most of the time. When in use, Silverthorne won't be able to spend nearly that much time in C6.

Despite the implementation of a C6 power state, Silverthorne will still lose to ARM based processors in both active and idle power. The active power disadvantage will be erased over the coming years as the microarchitecture evolves (and smaller manufacturing processes are implemented), while the idle power requires more of a platform approach. As we reported in our first Menlow/Silverthorne article:

"The idle power reduction will come through highly integrated platforms, like what we're describing with Moorestown. By getting rid of the PCI bus and replacing it with Intel's own custom low-power interface, Intel hopes to get idle power under control. The idea is that I/O ports will only be woken up when needed (similar to how the data lines on the Centrino FSB function), and what will result are platforms with multiple days of battery life when playing back music."

The final aspect of unique power management in Silverthorne falls upon its gridless clock distribution. Every single element within a microprocessor operates on the same clock, and making sure the same clock signal arrives at the exact same time across the many-mm^2 die is a difficult task. In conventional microprocessors, clock distribution is handled using a complex tree - which ends up eating over 30% of total microprocessor power. In-order designs allow the easier use of gridless clock distribution, which is a flat distribution using multiple clocks at the same time (instead of a tree/gridded design that is hierarchical).

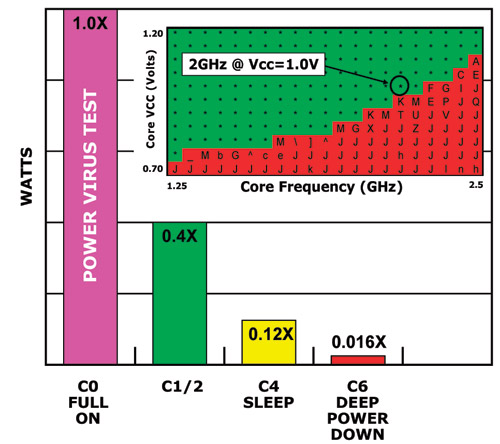

Intel is targeting 0.6W - 2.0W TDPs with Silverthorne - obviously depending on clock speeds. At 2.0GHz, running at 1.0V, Silverthorne runs at 90C and dissipates 2W. The CPU temperature alone should be an indication that this is too hot for an ultra small iPhone-like form factor, so expect to see devices that are closer to a PlayStation Portable in size and at lower clock speeds for most of them.

12 Comments

View All Comments

HelpfulVisitor - Wednesday, February 20, 2008 - link

Anand wrote the following:"The at 2.0GHz, running at 1.0V, Silverthorne runs at 90C and dissipates 2W. The CPU temperature alone should be indication that this is too hot for an ultra small iPhone-like form factor"

When the specs state TDP power at a given temperature, they are not claiming that the chip will dissipate that high of a temperature. They are baselining the TDP measurement, because leakage varies over different temperatures, and TDP needs to account for worst case conditions. It is standard practice to use the max Tcase temperature as a baseline, which is the temperature that the chip cannot exceed without permanent damage. Most chips operate WELL BELOW this.

While I cannot argue that Silverthorne would be inappropriate for iPhone, it is not because of the 90c degree specification. The 90c degree measurement only refers to where the thermal contraint specification has been measured.

stockascnc - Thursday, September 30, 2021 - link

NCFM Academy Hyderabad is one of the maximum properly know institutes now not simplest in Ameerpet but also in Hyderabad. <a href="https://www.ascncfmacademy.com/">Stock Market Training Institute in Hyderabad</a> We additionally offer Advanced Technical analysis training both on line and offline. We have designed the courses with years of experience and those publications will assure you success for sure. Just be part of the NCFM Academy Hyderabad if you need to research Advanced Technical Analysis. You can also study this course in Telugu too.Torched - Wednesday, February 20, 2008 - link

Going for the GeodeLX's jugular.puffpio - Wednesday, February 20, 2008 - link

Maybe Microsoft's answer to PSP and DS will use this hcipViRGE - Thursday, February 21, 2008 - link

I don't think so, the chip uses too much power. To give you an idea of the DS's power consumption, it comes with a 3.7v 1000mAh battery (in other words, 3.7watt-hours). Given that the DS lasts over 10 hours, you're looking at an average power consumption of 370mW for the entire device, meanwhile Silverthorne (just the CPU) is around 600mW before any other chips are added. The PSP/DS have the same power/thermal envelope as the iPhone, so you can count Silverthorne out of any similar device.Visual - Wednesday, February 20, 2008 - link

this just doesn't make sense... if it uses (and dissipates) less power than the scaled-down core cpus that are already in UMPCs, why would it's temperature be higher? why would it be harder to cool? why would it not be feasible for UMPCs?less is less, no matter how i look at it. i don't understand...

Visual - Wednesday, February 20, 2008 - link

oops, yeah. you said it wont be feasible for an iphone, not umpc.sorry i got confused... i guess it is just because i cant visualize the difference, not having seen either in person.

michael2k - Wednesday, February 20, 2008 - link

UMPC is about twice as big as an iPhone.UMPC is about half the size of an ultraportable laptop.

Calin - Wednesday, February 20, 2008 - link

"Inevitably the comparison to VIA's recently announced Isaiah CPU will be made, but Silverthorne is really aimed at a different market. Isaiah is a higher performance out-of-order core, while Silverthorne is eventually designed to make its way into highly integrated CE devices. We expect VIA's latest creation to outperform Silverthorne"I've never believed I'd live to see that - VIA outperforming Intel.

True, they might be targeting different power envelopes, but certainly Intel used to run circles around its competition from VIA

marsbound2024 - Wednesday, February 20, 2008 - link

On the "Who is Silverthorne" page, you repeated a paragraph talking about the sensibility of executing two IPC. Just wanted to throw that out there. :)