ISSCC

The annual IEEE International Solid-State Circuits Conference covers a range of topics of interest to AnandTech. Every year the conference includes a session on non-volatile memories where most of the NAND flash memory manufacturers share technical details of their latest developments. At the conference we get more information than these companies are usually willing to share in press briefings, and the presentations are usually about technology that will be hitting the market during the coming year. At ISSCC 2021 this week, four of the six major 3D NAND flash memory manufacturers are presenting their newest 3D NAND technology. Samsung, SK hynix and Kioxia (+Western Digital) are sharing their latest 3D TLC NAND designs and Intel is presenting their 144-layer 3D QLC NAND. Not participating this...

Samsung Launches Z-SSD SZ985: Up To 800GB Of Z-NAND

Samsung announced today that they are officially launching their first Z-SSD product, the SZ985. The Z-SSD uses Samsung's Z-NAND memory, a high-performance derivative of their 3D NAND flash memory...

45 by Billy Tallis on 1/29/2018AMD at ISSCC 2015: Carrizo and Excavator Details

AMD is using the International Solid-State Circuits Conference this week to present a paper and announce some interesting developments regarding the next iteration of the Bulldozer architecture, codenamed ‘Excavator’...

82 by Ian Cutress on 2/23/2015Intel at ISSCC 2015: Reaping the Benefits of 14nm and Going Beyond 10nm

As part of the International Solid-State Circuits Conference every year, Intel brings forward a number of presentations regarding its internal research. The theme this year at ISSCC is ‘Silicon...

55 by Ian Cutress on 2/22/2015Intel Reveals New Haswell Details at ISSCC 2014

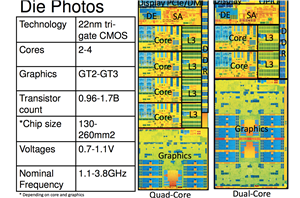

As of late, Intel has been unusually guarded about releasing information about its microprocessor designs. Haswell launched last year with great architecture disclosure, but very limited disclosure about die...

44 by Anand Lal Shimpi on 2/9/2014Intel at ISSCC '12: More Research into Near Threshold Voltage

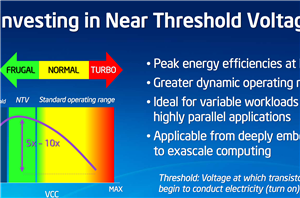

At IDF last year Intel's Justin Rattner demonstrated a 32nm test chip based on Intel's original Pentium architecture that could operate near its threshold voltage. The power consumption of...

13 by Anand Lal Shimpi on 2/20/2012Intel Demonstrates dual-core Atom SoC with Integrated WiFi Transceiver

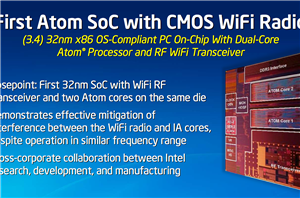

This week is the annual International Solid-State Circuits Conference (ISSCC) where chip companies from all walks of life present papers documenting everything from shipping architectures to future research projects...

9 by Anand Lal Shimpi on 2/20/2012